Since our establishment in 2007, we have successfully led numerous hardware design and verification projects to completion. In recent years, our business has expanded to encompass large-scale projects in AI, HPC (High-Performance Computing), and autonomous driving, where we have continued to deliver proven results.

Additionally, we have built strong, long-standing relationships with major OEMs, and in recent years, we have seen a growing number of requests from semiconductor manufacturers. This is a testament to the trust and confidence we have earned by consistently providing on-time, on-budget, and high-quality verification services.

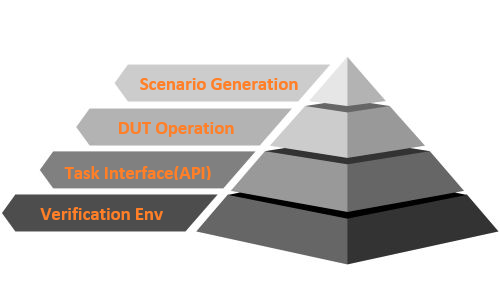

We offer comprehensive verification solutions to ensure the reliability and performance of complex designs.

Our proprietary solutions are designed to accelerate and enhance the verification process, leveraging our in-house development expertise.

Enhancing verification efficiency through constrained random testing and coverage-driven methodologies